# S25FL032P

Data Sheet

32-Mbit CMOS 3.0 Volt Flash Memory with 104-MHz SPI (Serial Peripheral Interface) Multi I/O Bus

**Notice to Readers:** This document states the current technical specifications regarding the Spansion product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See *Notice On Data Sheet Designations* for definitions.

## **Notice On Data Sheet Designations**

Spansion Inc. issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Spansion data sheet designations are presented here to highlight their presence and definitions.

#### Advance Information

The Advance Information designation indicates that Spansion Inc. is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Spansion Inc. therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Spansion Inc. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed product without notice."

#### **Preliminary**

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Spansion places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Spansion product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or V<sub>IO</sub> range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Spansion Inc. applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Spansion product(s) described herein. Spansion Inc. deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local sales office.

# S25FL032P

# 32-Mbit CMOS 3.0 Volt Flash Memory with 104-MHz SPI (Serial Peripheral Interface) Multi I/O Bus

Data Sheet

### **Distinctive Characteristics**

#### **Architectural Advantages**

- Single power supply operation

- Full voltage range: 2.7 to 3.6V read and write operations

- Memory architecture

- Uniform 64 KB sectors

- Top or bottom parameter block (Two 64-KB sectors (top or bottom) broken down into sixteen 4-KB sub-sectors each)

- 256-byte page size

- Backward compatible with the S25FL032A device

#### ■ Program

- Page Program (up to 256 bytes) in 1.5 ms (typical)

- Program operations are on a page by page basis

- Accelerated programming mode via 9V W#/ACC pin

- Quad Page Programming

#### ■ Erase

- Bulk erase function

- Sector erase (SE) command (D8h) for 64 KB sectors

- Sub-sector erase (P4E) command (20h) for 4 KB sectors

- Sub-sector erase (P8E) command (40h) for 8 KB sectors

#### ■ Cycling endurance

- 100,000 cycles per sector typical

#### ■ Data retention

- 20 years typical

#### ■ Device ID

- JEDEC standard two-byte electronic signature

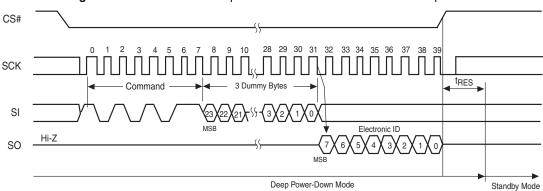

- RES command one-byte electronic signature for backward compatibility

- One time programmable (OTP) area for permanent, secure identification; can be programmed and locked at the factory or by the customer

# ■ CFI (Common Flash Interface) compliant: allows host system to identify and accommodate multiple flash devices

#### ■ Process technology

- Manufactured on 0.09 μm MirrorBit® process technology

#### ■ Package option

- Industry Standard Pinouts

- 8-pin SO package (208 mils)

- 16-pin SO package (300 mils)

- 8-contact USON package (5 x 6 mm)

- 8-contact WSON package (6 x 8 mm)

- 24-ball BGA 6 x 8 mm package, 5 x 5 pin configuration

- 24-ball BGA 6 x 8 mm package, 6 x 4 pin configuration

#### **Performance Characteristics**

#### ■ Speed

- Normal READ (Serial): 40 MHz clock rate

- FAST\_READ (Serial): 104 MHz clock rate (maximum)

- DUAL I/O FAST\_READ: 80 MHz clock rate or 20 MB/s effective data rate

- QUAD I/O FAST\_READ: 80 MHz clock rate or 40 MB/s effective data rate

#### ■ Power saving standby mode

- Standby Mode 80 µA (typical)

- Deep Power-Down Mode 3 µA (typical)

### **Memory Protection Features**

### ■ Memory protection

- W#/ACC pin works in conjunction with Status Register Bits to protect specified memory areas

- Status Register Block Protection bits (BP2, BP1, BP0) in status

## **General Description**

The S25FL032P is a 3.0 Volt (2.7V to 3.6V), single-power-supply Flash memory device. The device consists of 64 uniform 64 KB sectors with the two (Top or Bottom) 64 KB sectors further split up into thirty-two 4KB sub sectors. The S25FL032P device is fully backward compatible with the S25FL032A device.

The device accepts data written to SI (Serial Input) and outputs data on SO (Serial Output). The devices are designed to be programmed in-system with the standard system 3.0-volt  $V_{CC}$  supply.

The S25FL032P device adds the following high-performance features using 5 new instructions:

- Dual Output Read using both SI and SO pins as output pins at a clock rate of up to 80 MHz

- Quad Output Read using SI, SO, W#/ACC and HOLD# pins as output pins at a clock rate of up to 80 MHz

- Dual I/O High Performance Read using both SI and SO pins as input and output pins at a clock rate of up to 80 MHz

- Quad I/O High Performance Read using SI, SO, W#/ACC and HOLD# pins as input and output pins at a clock rate of up to 80 MHz

- Quad Page Programming using SI, SO, W#/ACC and HOLD# pins as input pins to program data at a clock rate of up to 80 MHz

The memory can be programmed 1 to 256 bytes at a time, using the Page Program command. The device supports Sector Erase and Bulk Erase commands.

Each device requires only a 3.0-volt power supply (2.7V to 3.6V) for both read and write functions. Internally generated and regulated voltages are provided for the program operations. This device requires a high voltage supply to the W#/ACC pin to enable the Accelerated Programming mode.

The S25FL032P device also offers a One-Time Programmable area (OTP) of up to 128-bits (16 bytes) for permanent secure identification and an additional 490 bytes of OTP space for other use. This OTP area can be programmed or read using the OTPP or OTPR instructions.

## Data Sheet

# **Table of Contents**

| Dist | inctive C           | Characteristics                                       | 3  |  |  |  |  |  |

|------|---------------------|-------------------------------------------------------|----|--|--|--|--|--|

| Gen  | General Description |                                                       |    |  |  |  |  |  |

| 1.   | Block D             | Diagram                                               | 9  |  |  |  |  |  |

| 2.   | Connec              | etion Diagrams                                        | Ĝ  |  |  |  |  |  |

| 3.   | Input/O             | utput Descriptions1                                   | 11 |  |  |  |  |  |

| 4.   | Logic S             | ymbol                                                 | 2  |  |  |  |  |  |

| 5.   | Orderin             | g Information                                         | 13 |  |  |  |  |  |

|      | 5.1                 | Valid Combinations                                    |    |  |  |  |  |  |

| 6.   | Spansi              | on SPI Modes                                          | 14 |  |  |  |  |  |

| 7.   | Device              | Operations                                            | 5  |  |  |  |  |  |

|      | 7.1                 | Byte or Page Programming                              |    |  |  |  |  |  |

|      | 7.2                 | Quad Page Programming 1                               | 5  |  |  |  |  |  |

|      | 7.3                 | Dual and Quad I/O Mode 1                              |    |  |  |  |  |  |

|      | 7.4                 | Sector Erase / Bulk Erase                             |    |  |  |  |  |  |

|      | 7.5                 | Monitoring Write Operations Using the Status Register |    |  |  |  |  |  |

|      | 7.6                 | Active Power and Standby Power Modes                  |    |  |  |  |  |  |

|      | 7.7                 | Status Register                                       |    |  |  |  |  |  |

|      | 7.8                 | Configuration Register                                |    |  |  |  |  |  |

|      | 7.9                 | Data Protection Modes                                 |    |  |  |  |  |  |

|      | 7.10                | Hold Mode (HOLD#)                                     |    |  |  |  |  |  |

|      | 7.11                | Accelerated Programming Operation                     | 9  |  |  |  |  |  |

| 8.   | Sector              | Address Table                                         | 20 |  |  |  |  |  |

| 9.   | Comma               | and Definitions 2                                     |    |  |  |  |  |  |

|      | 9.1                 | Read Data Bytes (READ) 2                              |    |  |  |  |  |  |

|      | 9.2                 | Read Data Bytes at Higher Speed (FAST_READ)           |    |  |  |  |  |  |

|      | 9.3                 | Dual Output Read Mode (DOR)                           |    |  |  |  |  |  |

|      | 9.4                 | Quad Output Read Mode (QOR)                           |    |  |  |  |  |  |

|      | 9.5                 | DUAL I/O High Performance Read Mode (DIOR)            |    |  |  |  |  |  |

|      | 9.6                 | Quad I/O High Performance Read Mode (QIOR)            |    |  |  |  |  |  |

|      | 9.7                 | Read Identification (RDID)                            |    |  |  |  |  |  |

|      | 9.8                 | Read-ID (READ_ID)                                     |    |  |  |  |  |  |

|      | 9.9                 | Write Enable (WREN)                                   |    |  |  |  |  |  |

|      | 9.10                | Write Disable (WRDI)                                  |    |  |  |  |  |  |

|      | 9.11                | Read Status Register (RDSR)                           |    |  |  |  |  |  |

|      | 9.12                | Read Configuration Register (RCR)                     |    |  |  |  |  |  |

|      | 9.13                | Write Registers (WRR)                                 |    |  |  |  |  |  |

|      | 9.14                | Page Program (PP)                                     |    |  |  |  |  |  |

|      | 9.15<br>9.16        |                                                       |    |  |  |  |  |  |

|      | 9.10                | Parameter Sector Erase (P4E, P8E)                     |    |  |  |  |  |  |

|      | 9.17                | Bulk Erase (BE)                                       |    |  |  |  |  |  |

|      | 9.19                | Deep Power-Down (DP)                                  |    |  |  |  |  |  |

|      | 9.20                | Release from Deep Power-Down (RES)                    |    |  |  |  |  |  |

|      | 9.21                | Clear Status Register (CLSR)                          |    |  |  |  |  |  |

|      | 9.22                | OTP Program (OTPP)                                    |    |  |  |  |  |  |

|      | 9.23                | Read OTP Data Bytes (OTPR)                            |    |  |  |  |  |  |

| 10.  | OTP Re              | gions5                                                | 50 |  |  |  |  |  |

|      | 10.1                | Programming OTP Address Space                         |    |  |  |  |  |  |

|      | 10.2                | Reading OTP Data                                      |    |  |  |  |  |  |

|      | 10.3                | Locking OTP Regions                                   |    |  |  |  |  |  |

| 11.  |                     | up and Power-down                                     |    |  |  |  |  |  |

|      |                     | •                                                     |    |  |  |  |  |  |

| 12.  | initial D           | elivery State                                         | 54 |  |  |  |  |  |

#### Data Sheet

| 13. | Program Acceleration via W#/ACC Pin 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14. | Electrical Specifications5514.1 Absolute Maximum Ratings55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15. | Operating Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16. | DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 17. | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18. | AC Characteristics 57 18.1 Capacitance 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

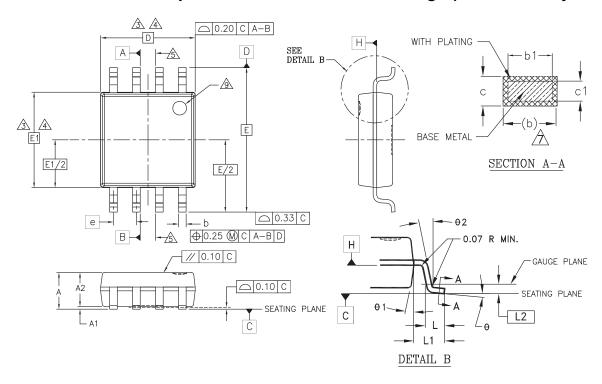

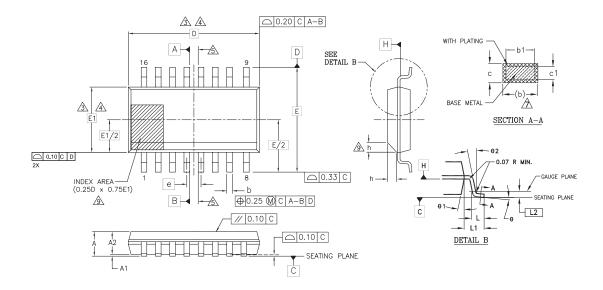

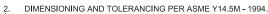

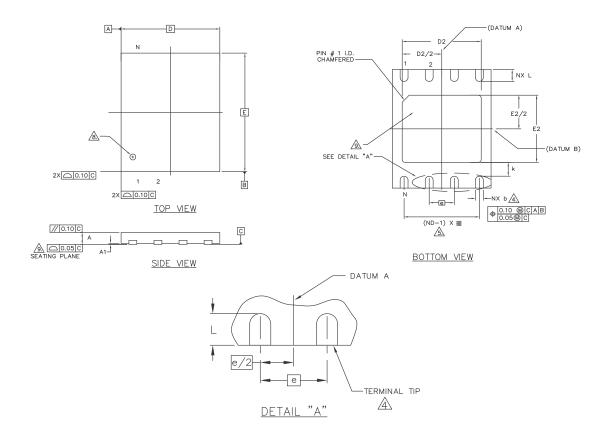

| 19. | Physical Dimensions       61         19.1       SOC008 wide — 8-pin Plastic Small Outline Package (208-mils Body Width)       61         19.2       SO3 016 — 16-pin Wide Plastic Small Outline Package (300-mil Body Width)       62         19.3       UNE008 — USON 8-contact (5 x 6 mm) No-Lead Package       63         19.4       WNF008 — WSON 8-contact (6 x 8 mm) No-Lead Package       64         19.5       FAB024 — 24-ball Ball Grid Array (6 x 8 mm) Package       65         19.6       FAC024 — 24-ball Ball Grid Array (6 x 8 mm) Package       66 |

| 20  | Revision History 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Figures**

| Figure 2.1                 | 16-pin Plastic Small Outline Package (SO)                         | . 9  |

|----------------------------|-------------------------------------------------------------------|------|

| Figure 2.2                 | 8-pin Plastic Small Outline Package (SO)                          | . 10 |

| Figure 2.3                 | 8-contact USON (5 x 6 mm) Package                                 |      |

| Figure 2.4                 | 8-contact WSON Package (6 x 8 mm)                                 |      |

| Figure 2.5                 | 6x8 mm 24-ball BGA Package, 5x5 pin Configuration                 |      |

| Figure 2.6                 | 6x8 mm 24-ball BGA Package, 6x4 pin Configuration                 |      |

| Figure 6.1                 | Bus Master and Memory Devices on the SPI Bus                      |      |

| Figure 6.2                 | SPI Modes Supported                                               |      |

| Figure 7.1                 | Hold Mode Operation                                               |      |

| Figure 9.1                 | Read Data Bytes (READ) Command Sequence                           |      |

| Figure 9.2                 | Read Data Bytes at Higher Speed (FAST_READ) Command Sequence      |      |

| Figure 9.3                 | Dual Output Read Instruction Sequence                             |      |

| Figure 9.4                 | Quad Output Read Instruction Sequence                             |      |

| Figure 9.5                 | DUAL I/O High Performance Read Instruction Sequence               |      |

| Figure 9.6                 | Continuous Dual I/O High Performance Read Instruction Sequence    |      |

| Figure 9.7                 | QUAD I/O High Performance Instruction Sequence                    |      |

| Figure 9.8                 | Continuous QUAD I/O High Performance Instruction Sequence         |      |

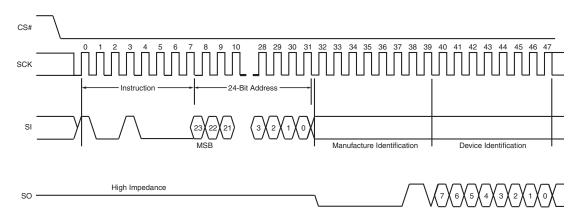

| Figure 9.9                 | Read Identification (RDID) Command Sequence and Data-Out Sequence |      |

| Figure 9.10                | Read-ID (RDID) Command Timing Diagram                             |      |

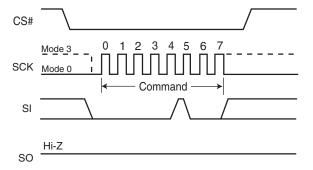

| Figure 9.11                | Write Enable (WREN) Command Sequence                              |      |

| Figure 9.12                | Write Disable (WRDI) Command Sequence                             |      |

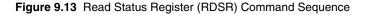

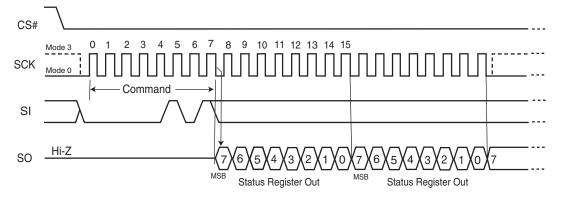

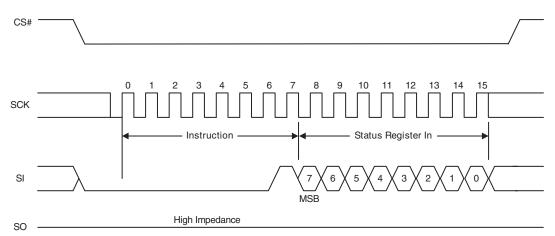

| Figure 9.13                | Read Status Register (RDSR) Command Sequence                      |      |

| Figure 9.14                | Read Configuration Register (RCR) Instruction Sequence            |      |

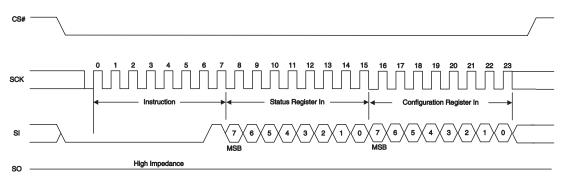

| Figure 9.15                | Write Registers (WRR) Instruction Sequence – 8 data bits          |      |

| Figure 9.16                | Write Registers (WRR) Instruction Sequence – 16 data bits         |      |

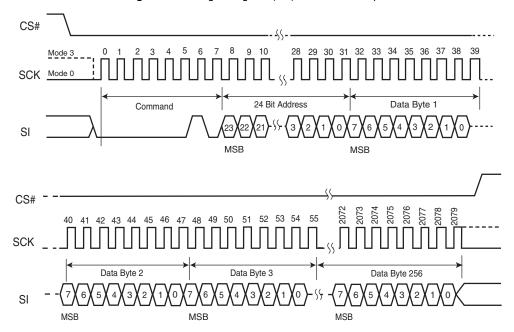

| Figure 9.17                | Page Program (PP) Command Sequence                                |      |

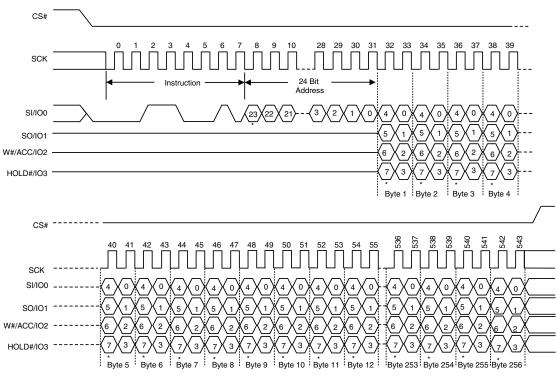

| Figure 9.18                | QUAD Page Program Instruction Sequence                            |      |

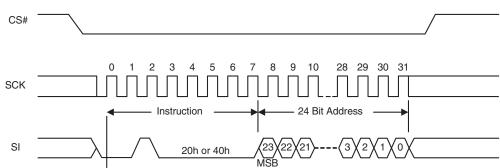

| Figure 9.19                | Parameter Sector Erase (P4E, P8E) Instruction Sequence            |      |

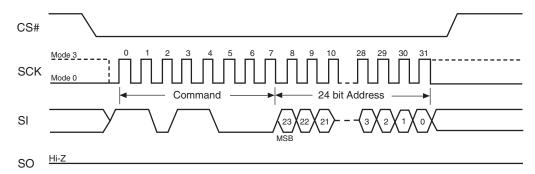

| Figure 9.20                | Sector Erase (SE) Command Sequence                                |      |

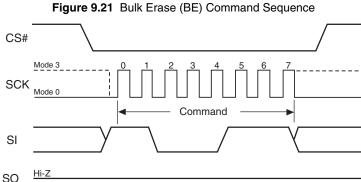

| Figure 9.21                | Bulk Erase (BE) Command Sequence                                  |      |

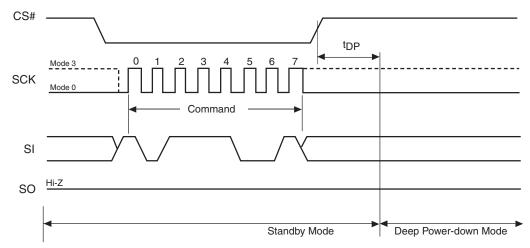

| Figure 9.22                | Deep Power-Down (DP) Command Sequence                             |      |

| Figure 9.23                | Release from Deep Power-Down (RES) Command Sequence               |      |

| Figure 9.24                | Release from Deep Power-Down and RES Command Sequence             |      |

| Figure 9.25<br>Figure 9.26 | OTP Program Instruction Sequence                                  |      |

| Figure 9.27                | Read OTP Instruction Sequence                                     |      |

| Figure 10.1                | OTP Memory Map - Part 1                                           |      |

| Figure 10.1                | OTP Memory Map - Part 2                                           |      |

| Figure 11.1                | Power-Up Timing Diagram                                           |      |

| Figure 11.2                | Power-down and Voltage Drop                                       |      |

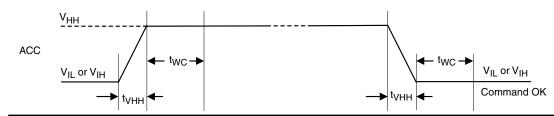

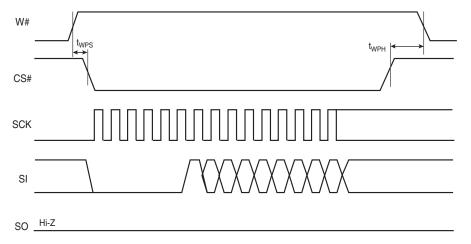

| Figure 13.1                | ACC Program Acceleration Timing Requirements                      |      |

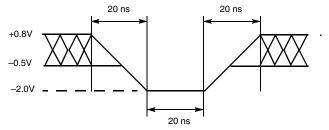

| Figure 14.1                | Maximum Negative Overshoot Waveform                               |      |

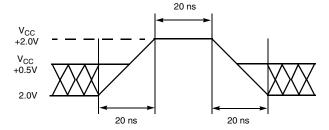

| Figure 14.2                | Maximum Positive Overshoot Waveform                               |      |

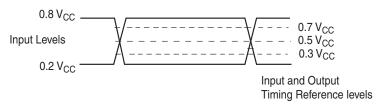

| Figure 17.1                | AC Measurements I/O Waveform                                      |      |

| Figure 18.1                | AC Characteristics                                                |      |

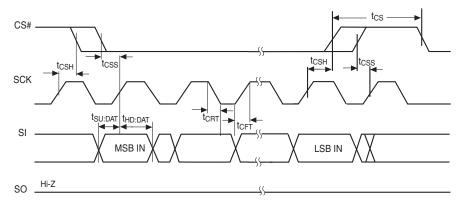

| Figure 18.2                | SPI Mode 0 (0,0) Input Timing                                     |      |

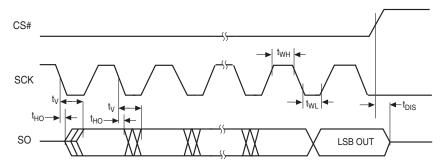

| Figure 18.3                | SPI Mode 0 (0,0) Output Timing                                    |      |

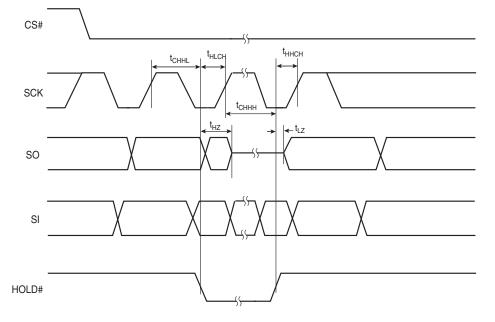

| Figure 18.4                | HOLD# Timing                                                      |      |

| Figure 18.5                | Write Protect Setup and Hold Timing during WRR when SRWD = 1      |      |

|                            |                                                                   |      |

# Data Sheet

# **Tables**

| Table 5.1  | S25FL032P Valid Combinations                             | 13 |

|------------|----------------------------------------------------------|----|

| Table 7.1  | Suggested Cross Settings                                 | 16 |

| Table 7.2  | Configuration Register Table                             | 17 |

| Table 7.3  | TBPROT = 0 (Starts Protection from TOP of Array)         | 18 |

| Table 7.4  | TBPROT=1 (Starts Protection from BOTTOM of Array)        | 18 |

| Table 8.1  | S25FL032P Sector Address Table TBPARM=0                  | 20 |

| Table 8.2  | S25FL032P Sector Address Table TBPARM=1                  | 21 |

| Table 9.1  | Instruction Set                                          | 23 |

| Table 9.2  | Manufacturer & Device ID - RDID (JEDEC 9Fh):             | 32 |

| Table 9.3  | Product Group CFI Query Identification String            | 32 |

| Table 9.4  | Product Group CFI System Interface String                | 32 |

| Table 9.5  | Product Group CFI Device Geometry Definition             | 33 |

| Table 9.6  | Product Group CFI Primary Vendor-Specific Extended Query | 34 |

| Table 9.7  | READ_ID Data-Out Sequence                                | 35 |

| Table 9.8  | S25FL032P Status Register                                | 37 |

| Table 9.9  | Protection Modes                                         | 40 |

| Table 10.1 | ESN1 and ESN2                                            | 50 |

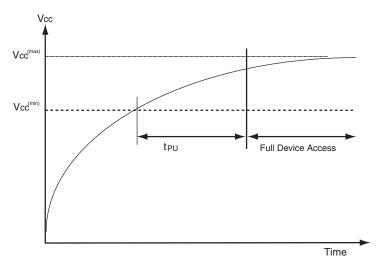

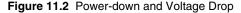

| Table 11.1 | Power-Up / Power-Down Voltage and Timing                 | 54 |

| Table 13.1 | ACC Program Acceleration Specifications                  | 54 |

| Table 15.1 | Operating Ranges                                         | 55 |

| Table 16.1 | DC Characteristics (CMOS Compatible)                     | 56 |

| Table 17.1 | Test Specifications                                      | 57 |

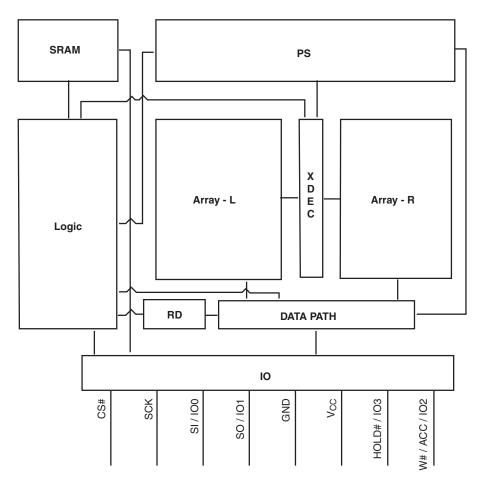

# 1. Block Diagram

# 2. Connection Diagrams

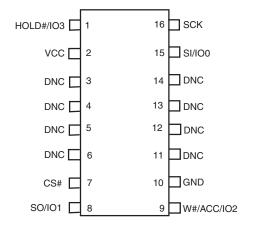

Figure 2.1 16-pin Plastic Small Outline Package (SO)

Note

DNC = Do Not Connect (Reserved for future use)

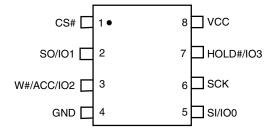

Figure 2.2 8-pin Plastic Small Outline Package (SO)

Figure 2.3 8-contact USON (5 x 6 mm) Package

#### Note

There is an exposed central pad on the underside of the USON package. This should not be connected to any voltage or signal line on the PCB. Connecting the central pad to GND ( $V_{SS}$ ) is possible, provided PCB routing ensures 0mV difference between voltage at the USON GND ( $V_{SS}$ ) lead and the central exposed pad.

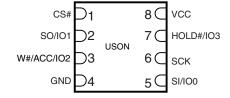

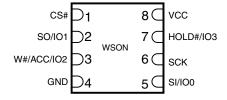

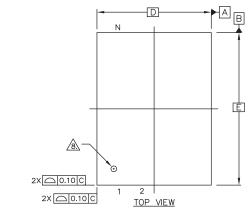

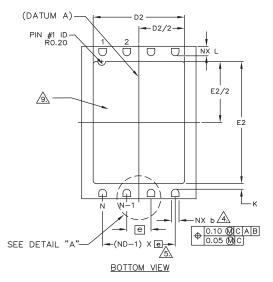

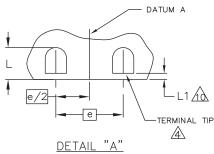

Figure 2.4 8-contact WSON Package (6 x 8 mm)

#### Note

There is an exposed central pad on the underside of the WSON package. This should not be connected to any voltage or signal line on the PCB. Connecting the central pad to GND  $(V_{SS})$  is possible, provided PCB routing ensures 0mV difference between voltage at the WSON GND  $(V_{SS})$  lead and the central exposed pad.

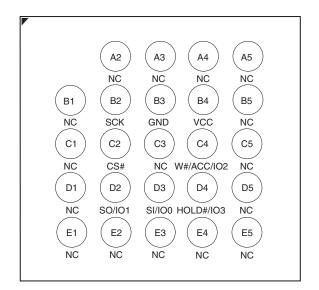

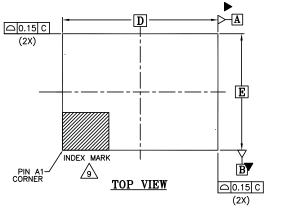

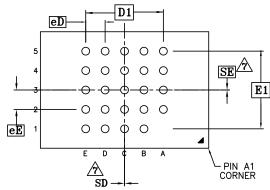

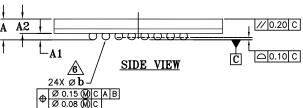

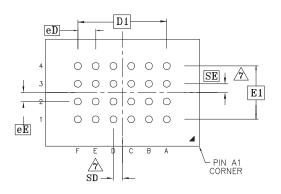

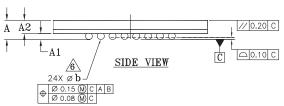

Figure 2.5 6x8 mm 24-ball BGA Package, 5x5 pin Configuration

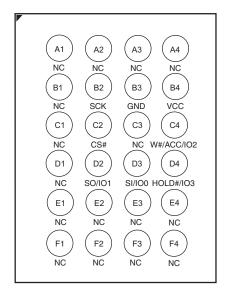

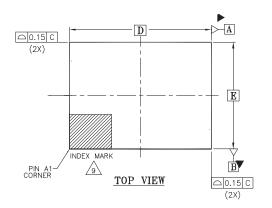

Figure 2.6 6x8 mm 24-ball BGA Package, 6x4 pin Configuration

# 3. Input/Output Descriptions

| Signal          | I/O   | Description                                                                                                                                                                                                                                                                                                               |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO/IO1          | I/O   | Serial Data Output: Transfers data serially out of the device on the falling edge of SCK. Functions as an input pin in Dual and Quad I/O, and Quad Page Program modes.                                                                                                                                                    |

| SI/IO0          | I/O   | Serial Data Input: Transfers data serially into the device. Device latches commands, addresses, and program data on SI on the rising edge of SCK. Functions as an output pin in Dual and Quad I/O mode.                                                                                                                   |

| SCK             | Input | Serial Clock: Provides serial interface timing. Latches commands, addresses, and data on SI on rising edge of SCK. Triggers output on SO after the falling edge of SCK.                                                                                                                                                   |

| CS#             | Input | Chip Select: Places device in active power mode when driven low. Deselects device and places SO at high impedance when high. After power-up, device requires a falling edge on CS# before any command is written. Device is in standby mode when a program, erase, or Write Status Register operation is not in progress. |

| HOLD#/IO3       | I/O   | <b>Hold</b> : Pauses any serial communication with the device without deselecting it. When driven low, SO is at high impedance, and all input at SI and SCK are ignored. Requires that CS# also be driven low. Functions as an output pin in Quad I/O mode.                                                               |

| W#/ACC/IO2      | I/O   | Write Protect: Protects the memory area specified by Status Register bits BP2:BP0. When driven low, prevents any program or erase command from altering the data in the protected memory area. Functions as an output pin in Quad I/O mode.                                                                               |

| V <sub>CC</sub> | Input | Supply Voltage                                                                                                                                                                                                                                                                                                            |

| GND             | Input | Ground                                                                                                                                                                                                                                                                                                                    |

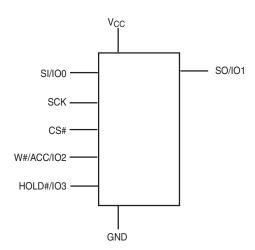

# 4. Logic Symbol

## 5. Ordering Information

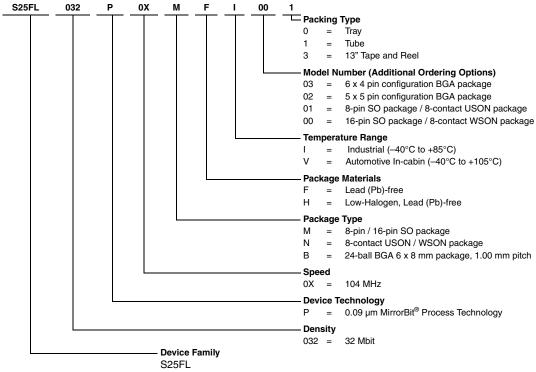

The ordering part number is formed by a valid combination of the following:

Spansion Memory 3.0 Volt-only, Serial Peripheral Interface (SPI) Flash Memory

### 5.1 Valid Combinations

Table 5.1 lists the valid combinations configurations planned to be supported in volume for this device.

Table 5.1 S25FL032P Valid Combinations

|                              | S25FL032     | P Valid Combinations     |                 |              |                         |  |

|------------------------------|--------------|--------------------------|-----------------|--------------|-------------------------|--|

| Base Ordering<br>Part Number | Speed Option | Package &<br>Temperature | Model<br>Number | Packing Type | Package Marking         |  |

|                              |              | MFI, NFI                 | 00. 01          | 0, 1, 3      |                         |  |

| S25FL032P                    | ox -         | MFV, NFV                 | 00, 01          | 0, 1, 3      | FL032P + (Temp) + F     |  |

| 323FL032F                    |              | BHI                      | 02. 03          | 0, 3         | - rLuszr + (lellip) + r |  |

|                              |              | BHV                      | 02, 03          | 0, 3         |                         |  |

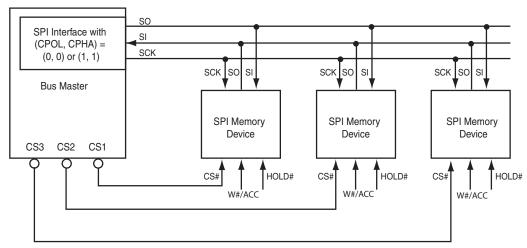

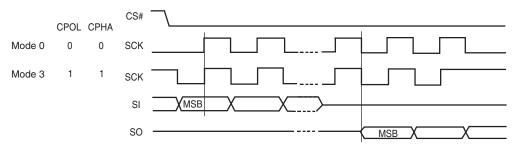

## 6. Spansion SPI Modes

A microcontroller can use either of its two SPI modes to control Spansion SPI Flash memory devices:

- CPOL = 0, CPHA = 0 (Mode 0)

- CPOL = 1, CPHA = 1 (Mode 3)

Input data is latched in on the rising edge of SCK, and output data is available from the falling edge of SCK for both modes.

When the bus master is in standby mode, SCK is as shown in Figure 6.2 for each of the two modes:

- SCK remains at 0 for (CPOL = 0, CPHA = 0 Mode 0)

- SCK remains at 1 for (CPOL = 1, CPHA = 1 Mode 3)

Figure 6.1 Bus Master and Memory Devices on the SPI Bus

#### Note

The Write Protect/Accelerated Programming (W#/ACC) and Hold (HOLD#) signals should be driven high (logic level 1) or low (logic level 0) as appropriate.

Figure 6.2 SPI Modes Supported

## 7. Device Operations

All Spansion SPI devices accept and output data in bytes (8 bits at a time). The SPI device is a slave device that supports an inactive clock while CS# is held low.

## 7.1 Byte or Page Programming

Programming data requires two commands: Write Enable (WREN), which is one byte, and a Page Program (PP) sequence, which consists of four bytes plus data. The Page Program sequence accepts from 1 byte up to 256 consecutive bytes of data (which is the size of one page) to be programmed in one operation. Programming means that bits can either be left at 0, or programmed from 1 to 0. Changing bits from 0 to 1 requires an erase operation.

## 7.2 Quad Page Programming

The Quad Page Program (QPP) instruction allows up to 256 bytes of data to be programmed using 4 pins as inputs at the same time, thus effectively quadrupling the data transfer rate, compared to the Page Program (PP) instruction. The Write Enable Latch (WEL) bit must be set to a 1 using the Write Enable (WREN) command prior to issuing the QPP command.

#### 7.3 Dual and Quad I/O Mode

The S25FL032P device supports Dual and Quad I/O operation when using the Dual/Quad Output Read Mode and the Dual/Quad I/O High Performance Mode instructions. Using the Dual or Quad I/O instructions allows data to be transferred to or from the device at two to four times the rate of standard SPI devices. When operating in the Dual or Quad I/O High Performance Mode (BBh or EBh instructions), data can be read at fast speed using two or four data bits at a time, and the 3-byte address can be input two or four address bits at a time.

### 7.4 Sector Erase / Bulk Erase

The Sector Erase (SE) and Bulk Erase (BE) commands set all the bits in a sector or the entire memory array to 1. While bits can be individually programmed from 1 to 0, erasing bits from 0 to 1 must be done on a sectorwide (SE) or array-wide (BE) level. In addition to the 64-KB Sector Erase (SE), the S25FL032P device also offers 4-KB Parameter Sector Erase (P4E) and 8-KB Parameter Sector Erase (P8E).

## 7.5 Monitoring Write Operations Using the Status Register

The host system can determine when a Write Register, program, or erase operation is complete by monitoring the Write in Progress (WIP) bit in the Status Register. The Read from Status Register command provides the state of the WIP bit. In addition, the S25FL032P device offers two additional bits in the Status Register (P\_ERR, E\_ERR) to indicate whether a Program or Erase operation was a success or failure.

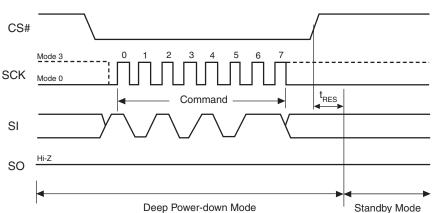

## 7.6 Active Power and Standby Power Modes

The device is enabled and in the Active Power mode when Chip Select (CS#) is Low. When CS# is high, the device is disabled, but may still be in the Active Power mode until all program, erase, and Write Registers operations have completed. The device then goes into the Standby Power mode, and power consumption drops to  $I_{SB}$ . The Deep Power-Down (DP) command provides additional data protection against inadvertent signals. After writing the DP command, the device ignores any further program or erase commands, and reduces its power consumption to  $I_{DP}$ .

### 7.7 Status Register

The Status Register contains the status and control bits that can be read or set by specific commands (see Table 9.1 on page 23). These bits configure different protection configurations and supply information of operation of the device. (for details see Table 9.8, *S25FL032P Status Register* on page 37):

- Write In Progress (WIP): Indicates whether the device is performing a Write Registers, program or erase operation.

- Write Enable Latch (WEL): Indicates the status of the internal Write Enable Latch.

- Block Protect (BP2, BP1, BP0): Non-volatile bits that define memory area to be software-protected against program and erase commands.

- Erase Error (E\_ERR): The Erase Error Bit is used as an Erase operation success and failure check.

- Program Error (P\_ERR): The Program Error Bit is used as an program operation success and failure check.

- Status Register Write Disable (SRWD): Places the device in the Hardware Protected mode when this bit is set to 1 and the W#/ACC input is driven low. In this mode, the non-volatile bits of the Status Register (SRWD, BP2, BP1, BP0) become read-only bits.

## 7.8 Configuration Register

The Configuration Register contains the control bits that can be read or set by specific commands. These bits configure different configurations and security features of the device.

- The FREEZE bit locks the BP2-0 bits in Status Register and the TBPROT and TBPARM bits in the Configuration Register. Note that once the FREEZE bit has been set to '1', then it cannot be cleared to '0' until a power-on-reset is executed. As long as the FREEZE bit is set to '0', then the other bits of the Configuration Register, including FREEZE bit, can be written to.

- The QUAD bit is non-volatile and sets the pin out of the device to Quad mode; that is, W#/ACC becomes IO2 and HOLD# becomes IO3. The instructions for Serial, Dual Output, and Dual I/O reads function as normal. The W#/ACC and HOLD# functionality does not work when the device is set in Quad mode.

- The TBPARM bit defines the logical location of the 4 KB parameter sectors. The parameter sectors consist of thirty two 4 KB sectors. All sectors other than the parameter sectors are defined to be 64-KB uniform in size. When TBPARM is set to a '1', the 4 KB parameter sectors starts at the top of the array. When TBPARM is set to a '0', the 4 KB parameter sectors starts at the bottom of the array. Note that once this bit is set to a '1', it cannot be changed back to '0'.

- The BPNV bit defines whether or not the BP2-0 bits in the Status Register are volatile or non-volatile. When BPNV is set to a '1', the BP2-0 bits in the Status Register are volatile and will be reset to binary 111 after power on reset. When BPNV is set to a '0', the BP2-0 bits in the Status Register are non-volatile. Note that once this bit is set to a '1', it cannot be changed back to '0'.

- The TBPROT bit defines the operation of the block protection bits BP2, BP1, and BP0 in the Status Register. When TBPROT is set to a '0', then the block protection is defined to start from the top of the array. When TBPROT is set to a '1', then the block protection is defined to start from the bottom of the array. Note that once this bit is set to a '1', it cannot be changed back to '0'.

**Note**: It is suggested that the Block Protection and Parameter sectors not be set to the same area of the array; otherwise, the user cannot utilize the Parameter sectors if they are protected. The following matrix shows the recommended settings.

Table 7.1 Suggested Cross Settings

| TBPARM | TBPROT | Array Overview                                                                                   |

|--------|--------|--------------------------------------------------------------------------------------------------|

| 0      | 0      | Parameter Sectors – Bottom<br>BP Protection – Top<br>(default)                                   |

| 0      | 1      | Not recommended (Parameters & BP Protection are both Bottom)                                     |

| 1      | 0      | Not recommended (parameters & BP Protection are both Top)                                        |

| 1      | 1      | Parameter Sectors - Top of Array (high address)<br>BP Protection - Bottom of Array (low address) |

Table 7.2 Configuration Register Table

| Bit | Bit Name | Bit Function                                 | Description                                                              |  |  |

|-----|----------|----------------------------------------------|--------------------------------------------------------------------------|--|--|

| 7   | NA       | -                                            | Not Used                                                                 |  |  |

| 6   | NA       | -                                            | Not Used                                                                 |  |  |

| 5   | TBPROT   | Configures start of block protection         | 1 = Bottom Array (low address)<br>0 = Top Array (high address) (Default) |  |  |

| 4   | NA       | -                                            | Do not use                                                               |  |  |

| 3   | BPNV     | Configures BP2-0 bits in the Status Register | 1 = Volatile<br>0 = Non-volatile (Default)                               |  |  |

| 2   | TBPARM   | Configures Parameter sector location         | 1 = Top Array (high address)<br>0 = Bottom Array (low address) (Default) |  |  |

| 1   | QUAD     | Puts the device into Quad I/O mode           | 1 = Quad I/O<br>0 = Dual or Serial I/O (Default)                         |  |  |

| 0   | FREEZE   | Locks BP2-0 bits in the Status Register      | 1 = Enabled<br>0 = Disabled (Default)                                    |  |  |

#### Note

(Default) indicates the value of each Configuration Register bit set upon initial factory shipment.

### 7.9 Data Protection Modes

Spansion SPI Flash memory devices provide the following data protection methods:

- The Write Enable (WREN) command: Must be written prior to any command that modifies data. The WREN command sets the Write Enable Latch (WEL) bit. The WEL bit resets (disables writes) on power-up or after the device completes the following commands:

- Page Program (PP)

- Sector Erase (SE)

- Bulk Erase (BE)

- Write Disable (WRDI)

- Write Register (WRR)

- Parameter 4 KB Sector Erase (P4E)

- Parameter 8 KB Sector Erase (P8E)

- Quad Page Programming (QPP)

- OTP Byte Programming (OTPP)

- Software Protected Mode (SPM): The Block Protect (BP2, BP1, BP0) bits define the section of the memory array that can be read but not programmed or erased. Table 7.3 and Table 7.4 shows the sizes and address ranges of protected areas that are defined by Status Register bits BP2:BP0.

- Hardware Protected Mode (HPM): The Write Protect (W#/ACC) input and the Status Register Write Disable (SRWD) bit together provide write protection.

- Clock Pulse Count: The device verifies that all program, erase, and Write Register commands consist of a clock pulse count that is a multiple of eight before executing them.

| Status Register Block |   |     | Memory Array               |                                               |                 |                        |                                    |  |

|-----------------------|---|-----|----------------------------|-----------------------------------------------|-----------------|------------------------|------------------------------------|--|

| BP2 BP1 BP0           |   | BP0 | Protected<br>Address Range | Protected Unprotected e Sectors Address Range |                 | Unprotected<br>Sectors | Portion of<br>Total Memory<br>Area |  |

| 0                     | 0 | 0   | None                       | 0                                             | 000000h-3FFFFFh | SA63:SA0               | 0                                  |  |

| 0                     | 0 | 1   | 3F0000h-3FFFFFh            | (1) SA63                                      | 000000h-3EFFFFh | SA62:SA0               | 1/64                               |  |

| 0                     | 1 | 0   | 3E0000h-3FFFFFh            | (2) SA63:SA62                                 | 000000h-3DFFFFh | SA61:SA0               | 1/32                               |  |

| 0                     | 1 | 1   | 3C0000h-3FFFFFh            | (4) SA63:SA60                                 | 000000h-3BFFFFh | SA59:SA0               | 1/16                               |  |

| 1                     | 0 | 0   | 380000h-3FFFFFh            | (8) SA63:SA56                                 | 000000h-37FFFFh | SA55:SA0               | 1/8                                |  |

| 1                     | 0 | 1   | 300000h-3FFFFFh            | (16) SA63:SA48                                | 000000h-2FFFFFh | SA47:SA0               | 1/4                                |  |

| 1                     | 1 | 0   | 200000h-3FFFFFh            | (32) SA63:SA32                                | 000000h-1FFFFFh | SA31:SA0               | 1/2                                |  |

**Table 7.3** TBPROT = 0 (Starts Protection from TOP of Array)

**Table 7.4** TBPROT=1 (Starts Protection from BOTTOM of Array)

(64) SA63:SA0

| Status Register Block |     |     |                            | Protected            |                              |                        |                                    |

|-----------------------|-----|-----|----------------------------|----------------------|------------------------------|------------------------|------------------------------------|

| BP2                   | BP1 | BP0 | Protected<br>Address Range | Protected<br>Sectors | Unprotected<br>Address Range | Unprotected<br>Sectors | Portion of<br>Total Memory<br>Area |

| 0                     | 0   | 0   | None                       | 0                    | 000000h-3FFFFFh              | SA0:SA63               | 0                                  |

| 0                     | 0   | 1   | 000000h-00FFFFh            | (1) SA0              | 010000h-3FFFFFh              | SA1:SA63               | 1/64                               |

| 0                     | 1   | 0   | 000000h-01FFFFh            | (2) SA0:SA1          | 020000h-3FFFFFh              | SA2:SA63               | 1/32                               |

| 0                     | 1   | 1   | 000000h-03FFFFh            | (4) SA0:SA3          | 040000h-3FFFFFh              | SA4:SA63               | 1/16                               |

| 1                     | 0   | 0   | 000000h-07FFFFh            | (8) SA0:SA7          | 080000h-3FFFFFh              | SA8:SA63               | 1/8                                |

| 1                     | 0   | 1   | 000000h-0FFFFh             | (16) SA0:SA15        | 100000h-3FFFFFh              | SA16:SA63              | 1/4                                |

| 1                     | 1   | 0   | 000000h-1FFFFFh            | (32) SA0:SA31        | 200000h-3FFFFFh              | SA32:SA63              | 1/2                                |

| 1                     | 1   | 1   | 000000h-3FFFFFh            | (64) SA0:SA63        | None                         | None                   | ALL                                |

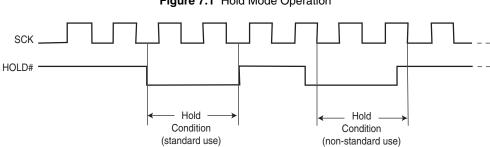

## 7.10 Hold Mode (HOLD#)

The Hold input (HOLD#) stops any serial communication with the device, but does not terminate any Write Registers, program or erase operation that is currently in progress.

The Hold mode starts on the falling edge of HOLD# if SCK is also low (see Figure 7.1, standard use). If the falling edge of HOLD# does not occur while SCK is low, the Hold mode begins after the next falling edge of SCK (non-standard use).

The Hold mode ends on the rising edge of HOLD# signal (standard use) if SCK is also low. If the rising edge of HOLD# does not occur while SCK is low, the Hold mode ends on the next falling edge of CLK (non-standard use) See Figure 7.1.

The SO output is high impedance, and the SI and SCK inputs are ignored (don't care) for the duration of the Hold mode.

CS# must remain low for the entire duration of the Hold mode to ensure that the device internal logic remains unchanged. If CS# goes high while the device is in the Hold mode, the internal logic is reset. To prevent the device from reverting to the Hold mode when device communication is resumed, HOLD# must be held high, followed by driving CS# low.

Note: The HOLD Mode feature is disabled during Quad I/O Mode.

000000h-3FFFFFh

None

None

All

Figure 7.1 Hold Mode Operation

# 7.11 Accelerated Programming Operation

The device offers accelerated program operations through the ACC function. This function is primarily intended to allow faster manufacturing throughput at the factory. If the system asserts  $V_{HH}$  on this pin, the device uses the higher voltage on the pin to reduce the time required for program operations. Removing  $V_{HH}$  from the W#/ACC pin returns the device to normal operation. Note that the W#/ACC pin must not be at  $V_{HH}$  for operations other than accelerated programming, or device damage may result. In addition, the W#/ACC pin must not be left floating or unconnected; inconsistent behavior of the device may result.

Note: The ACC function is disabled during Quad I/O Mode.

# 8. Sector Address Table

The Sector Address tables show the size of the memory array, sectors, and pages. The device uses pages to cache the program data before the data is programmed into the memory array. Each page or byte can be individually programmed (bits are changed from 1 to 0). The data is erased (bits are changed from 0 to 1) on a sub-sector, sector- or device-wide basis using the P4E/P8E, SE or BE commands. Table 8.1 and Table 8.2 show the starting and ending address for each sector. The complete set of sectors comprises the memory array of the Flash device.

Table 8.1 S25FL032P Sector Address Table TBPARM=0

| Sector | Address range |             | Sector | Address range |             | Sector | Address range |             |  |

|--------|---------------|-------------|--------|---------------|-------------|--------|---------------|-------------|--|

| Sector | Start address | End address | Sector | Start address | End address | Sector | Start address | End address |  |

| SA63   | 3F0000h       | 3FFFFFh     | SA31   | 1F0000h       | 1FFFFFh     | SS31   | 01F000h       | 01FFFFh     |  |

| SA62   | 3E0000h       | 3EFFFFh     | SA30   | 1E0000h       | 1EFFFFh     | SS30   | 01E000h       | 01EFFFh     |  |

| SA61   | 3D0000h       | 3DFFFFh     | SA29   | 1D0000h       | 1DFFFFh     | SS29   | 01D000h       | 01DFFFh     |  |

| SA60   | 3C0000h       | 3CFFFFh     | SA28   | 1C0000h       | 1CFFFFh     | SS28   | 01C000h       | 01CFFFh     |  |

| SA59   | 3B0000h       | 3BFFFFh     | SA27   | 1B0000h       | 1BFFFFh     | SS27   | 01B000h       | 01BFFFh     |  |

| SA58   | 3A0000h       | 3AFFFFh     | SA26   | 1A0000h       | 1AFFFFh     | SS26   | 01A000h       | 01AFFFh     |  |

| SA57   | 390000h       | 39FFFFh     | SA25   | 190000h       | 19FFFFh     | SS25   | 019000h       | 019FFFh     |  |

| SA56   | 380000h       | 38FFFFh     | SA24   | 180000h       | 18FFFFh     | SS24   | 018000h       | 018FFFh     |  |

| SA55   | 370000h       | 37FFFFh     | SA23   | 170000h       | 17FFFFh     | SS23   | 017000h       | 017FFFh     |  |

| SA54   | 360000h       | 36FFFFh     | SA22   | 160000h       | 16FFFFh     | SS22   | 016000h       | 016FFFh     |  |

| SA53   | 350000h       | 35FFFFh     | SA21   | 150000h       | 15FFFFh     | SS21   | 015000h       | 015FFFh     |  |

| SA52   | 340000h       | 34FFFFh     | SA20   | 140000h       | 14FFFFh     | SS20   | 014000h       | 014FFFh     |  |

| SA51   | 330000h       | 33FFFFh     | SA19   | 130000h       | 13FFFFh     | SS19   | 013000h       | 013FFFh     |  |

| SA50   | 320000h       | 32FFFFh     | SA18   | 120000h       | 12FFFFh     | SS18   | 012000h       | 012FFFh     |  |

| SA49   | 310000h       | 31FFFFh     | SA17   | 110000h       | 11FFFFh     | SS17   | 011000h       | 011FFFh     |  |

| SA48   | 300000h       | 30FFFFh     | SA16   | 100000h       | 10FFFFh     | SS16   | 010000h       | 010FFFh     |  |

| SA47   | 2F0000h       | 2FFFFFh     | SA15   | 0F0000h       | 0FFFFh      | SS15   | 00F000h       | 00FFFFh     |  |

| SA46   | 2E0000h       | 2EFFFFh     | SA14   | 0E0000h       | 0EFFFFh     | SS14   | 00E000h       | 00EFFFh     |  |

| SA45   | 2D0000h       | 2DFFFFh     | SA13   | 0D0000h       | 0DFFFFh     | SS13   | 00D000h       | 00DFFFh     |  |

| SA44   | 2C0000h       | 2CFFFFh     | SA12   | 0C0000h       | 0CFFFFh     | SS12   | 00C000h       | 00CFFFh     |  |

| SA43   | 2B0000h       | 2BFFFFh     | SA11   | 0B0000h       | 0BFFFFh     | SS11   | 00B000h       | 00BFFFh     |  |

| SA42   | 2A0000h       | 2AFFFFh     | SA10   | 0A0000h       | 0AFFFFh     | SS10   | 00A000h       | 00AFFFh     |  |

| SA41   | 290000h       | 29FFFFh     | SA9    | 090000h       | 09FFFFh     | SS9    | 009000h       | 009FFFh     |  |

| SA40   | 280000h       | 28FFFFh     | SA8    | 080000h       | 08FFFFh     | SS8    | 008000h       | 008FFFh     |  |

| SA39   | 270000h       | 27FFFFh     | SA7    | 070000h       | 07FFFFh     | SS7    | 007000h       | 007FFFh     |  |

| SA38   | 260000h       | 26FFFFh     | SA6    | 060000h       | 06FFFFh     | SS6    | 006000h       | 006FFFh     |  |

| SA37   | 250000h       | 25FFFFh     | SA5    | 050000h       | 05FFFFh     | SS5    | 005000h       | 005FFFh     |  |

| SA36   | 240000h       | 24FFFFh     | SA4    | 040000h       | 04FFFFh     | SS4    | 004000h       | 004FFFh     |  |

| SA35   | 230000h       | 23FFFFh     | SA3    | 030000h       | 03FFFFh     | SS3    | 003000h       | 003FFFh     |  |

| SA34   | 220000h       | 22FFFFh     | SA2    | 020000h       | 02FFFFh     | SS2    | 002000h       | 002FFFh     |  |

| SA33   | 210000h       | 21FFFFh     | SA1    | 010000h       | 01FFFFh     | SS1    | 001000h       | 001FFFh     |  |

| SA32   | 200000h       | 20FFFFh     | SA0    | 000000h       | 00FFFFh     | SS0    | 000000h       | 000FFFh     |  |

#### Note

Sector SA0 is split up into sub-sectors SS0 - SS15 (dark gray shading) Sector SA1 is split up into sub-sectors SS16 - SS31(light gray shading)

S25FL032P

Table 8.2 S25FL032P Sector Address Table TBPARM=1

| 01     | Address       | Range       | Sector | Address Range |             | 0      | Address Range |             |  |

|--------|---------------|-------------|--------|---------------|-------------|--------|---------------|-------------|--|

| Sector | Start Address | End Address | Sector | Start Address | End Address | Sector | Start Address | End Address |  |

| SS31   | 3FF000h       | 3FFFFFh     | SA63   | 3F0000h       | 3FFFFFh     | SA31   | 1F0000h       | 1FFFFFh     |  |

| SS30   | 3FE000h       | 3FEFFFh     | SA62   | 3E0000h       | 3EFFFFh     | SA30   | 1E0000h       | 1EFFFFh     |  |

| SS29   | 3FD000h       | 3FDFFFh     | SA61   | 3D0000h       | 3DFFFFh     | SA29   | 1D0000h       | 1DFFFFh     |  |

| SS28   | 3FC000h       | 3FCFFFh     | SA60   | 3C0000h       | 3CFFFFh     | SA28   | 1C0000h       | 1CFFFFh     |  |

| SS27   | 3FB000h       | 3FBFFFh     | SA59   | 3B0000h       | 3BFFFFh     | SA27   | 1B0000h       | 1BFFFFh     |  |

| SS26   | 3FA000h       | 3FAFFFh     | SA58   | 3A0000h       | 3AFFFFh     | SA26   | 1A0000h       | 1AFFFFh     |  |

| SS25   | 3F9000h       | 3F9FFFh     | SA57   | 390000h       | 39FFFFh     | SA25   | 190000h       | 19FFFFh     |  |

| SS24   | 3F8000h       | 3F8FFFh     | SA56   | 380000h       | 38FFFFh     | SA24   | 180000h       | 18FFFFh     |  |

| SS23   | 3F7000h       | 3F7FFFh     | SA55   | 370000h       | 37FFFFh     | SA23   | 170000h       | 17FFFFh     |  |

| SS22   | 3F6000h       | 3F6FFFh     | SA54   | 360000h       | 36FFFFh     | SA22   | 160000h       | 16FFFFh     |  |

| SS21   | 3F5000h       | 3F5FFFh     | SA53   | 350000h       | 35FFFFh     | SA21   | 150000h       | 15FFFFh     |  |

| SS20   | 3F4000h       | 3F4FFFh     | SA52   | 340000h       | 34FFFFh     | SA20   | 140000h       | 14FFFFh     |  |

| SS19   | 3F3000h       | 3F3FFFh     | SA51   | 330000h       | 33FFFFh     | SA19   | 130000h       | 13FFFFh     |  |

| SS18   | 3F2000h       | 3F2FFFh     | SA50   | 320000h       | 32FFFFh     | SA18   | 120000h       | 12FFFFh     |  |

| SS17   | 3F1000h       | 3F1FFFh     | SA49   | 310000h       | 31FFFFh     | SA17   | 110000h       | 11FFFFh     |  |

| SS16   | 3F0000h       | 3F0FFFh     | SA48   | 300000h       | 30FFFFh     | SA16   | 100000h       | 10FFFFh     |  |

| SS15   | 3EF000h       | 3EFFFFh     | SA47   | 2F0000h       | 2FFFFFh     | SA15   | 0F0000h       | 0FFFFFh     |  |

| SS14   | 3EE000h       | 3EEFFFh     | SA46   | 2E0000h       | 2EFFFFh     | SA14   | 0E0000h       | 0EFFFFh     |  |

| SS13   | 3ED000h       | 3EDFFFh     | SA45   | 2D0000h       | 2DFFFFh     | SA13   | 0D0000h       | 0DFFFFh     |  |

| SS12   | 3EC000h       | 3ECFFFh     | SA44   | 2C0000h       | 2CFFFFh     | SA12   | 0C0000h       | 0CFFFFh     |  |

| SS11   | 3EB000h       | 3EBFFFh     | SA43   | 2B0000h       | 2BFFFFh     | SA11   | 0B0000h       | 0BFFFFh     |  |

| SS10   | 3EA000h       | 3EAFFFh     | SA42   | 2A0000h       | 2AFFFFh     | SA10   | 0A0000h       | 0AFFFFh     |  |

| SS9    | 3E9000h       | 3E9FFFh     | SA41   | 290000h       | 29FFFFh     | SA9    | 090000h       | 09FFFFh     |  |

| SS8    | 3E8000h       | 3E8FFFh     | SA40   | 280000h       | 28FFFFh     | SA8    | 080000h       | 08FFFFh     |  |

| SS7    | 3E7000h       | 3E7FFFh     | SA39   | 270000h       | 27FFFFh     | SA7    | 070000h       | 07FFFFh     |  |

| SS6    | 3E6000h       | 3E6FFFh     | SA38   | 260000h       | 26FFFFh     | SA6    | 060000h       | 06FFFFh     |  |

| SS5    | 3E5000h       | 3E5FFFh     | SA37   | 250000h       | 25FFFFh     | SA5    | 050000h       | 05FFFFh     |  |

| SS4    | 3E4000h       | 3E4FFFh     | SA36   | 240000h       | 24FFFFh     | SA4    | 040000h       | 04FFFFh     |  |

| SS3    | 3E3000h       | 3E3FFFh     | SA35   | 230000h       | 23FFFFh     | SA3    | 030000h       | 03FFFFh     |  |

| SS2    | 3E2000h       | 3E2FFFh     | SA34   | 220000h       | 22FFFFh     | SA2    | 020000h       | 02FFFFh     |  |

| SS1    | 3E1000h       | 3E1FFFh     | SA33   | 210000h       | 21FFFFh     | SA1    | 010000h       | 01FFFFh     |  |

| SS0    | 3E0000h       | 3E0FFFh     | SA32   | 200000h       | 20FFFFh     | SA0    | 000000h       | 00FFFFh     |  |

### Note

Sector SA62 is split up into sub-sectors SS0 - SS15 (dark gray shading) Sector SA63 is split up into sub-sectors SS16 - SS31 (light gray shading)

## 9. Command Definitions

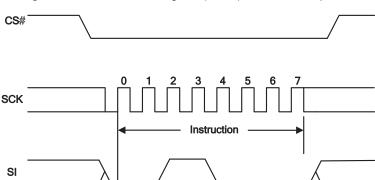

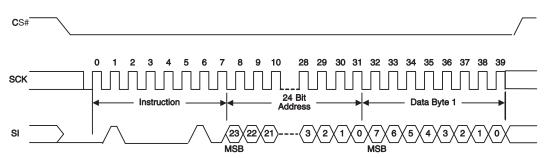

The host system must shift all commands, addresses, and data in and out of the device, beginning with the most significant bit. On the first rising edge of SCK after CS# is driven low, the device accepts the one-byte command on SI (all commands are one byte long), most significant bit first. Each successive bit is latched on the rising edge of SCK. Table 9.1 lists the complete set of commands.

Every command sequence begins with a one-byte command code. The command may be followed by address, data, both, or nothing, depending on the command. CS# must be driven high after the last bit of the command sequence has been written.

The Read Data Bytes (READ), Read Data Bytes at Higher Speed (FAST\_READ), Dual Output Read (DOR), Quad Output Read (QOR), Dual I/O High Performance Read (DIOR), Quad I/O High Performance Read (QIOR), Read Status Register (RDSR), Read Configuration Register (RCR), Read OTP Data (OTPR), Read Manufacturer and Device ID (READ\_ID), Read Identification (RDID) and Release from Deep Power-Down and Read Electronic Signature (RES) command sequences are followed by a data output sequence on SO. CS# can be driven high after any bit of the sequence is output to terminate the operation.

The Page Program (PP), Quad Page Program (QPP), 64 KB Sector Erase (SE), 4 KB Parameter Sector Erase (P4E), 8 KB Parameter Sector Erase (P8E), Bulk Erase (BE), Write Status and Configuration Registers (WRR), Program OTP space (OTPP), Write Enable (WREN), or Write Disable (WRDI) commands require that CS# be driven high at a byte boundary, otherwise the command is not executed. Since a byte is composed of eight bits, CS# must therefore be driven high when the number of clock pulses after CS# is driven low is an exact multiple of eight.

The device ignores any attempt to access the memory array during a Write Registers, program, or erase operation, and continues the operation uninterrupted.

The instruction set is listed in Table 9.1.

Table 9.1 Instruction Set

| Operation     | Command   | One byte Command<br>Code              | Description                                                                       | Address<br>Byte Cycle | Mode<br>Bit<br>Cycle | Dummy<br>Byte Cycle | Data<br>Byte<br>Cycle |

|---------------|-----------|---------------------------------------|-----------------------------------------------------------------------------------|-----------------------|----------------------|---------------------|-----------------------|

|               | READ      | (03h) 0000 0011                       | Read Data bytes                                                                   | 3                     | 0                    | 0                   | 1 to ∞                |

|               | FAST_READ | (0Bh) 0000 1011                       | Read Data bytes at Fast Speed                                                     | 3                     | 0                    | 1                   | 1 to ∞                |

|               | DOR       | (3Bh) 0011 1011                       | Dual Output Read                                                                  | 3                     | 0                    | 1                   | 1 to ∞                |

|               | QOR       | (6Bh) 0110 1011                       | Quad Output Read                                                                  | 3                     | 0                    | 1                   | 1 to ∞                |

| Read          | DIOR      | (BBh) 1011 1011                       | Dual I/O High Performance Read                                                    | 3                     | 1                    | 0                   | 1 to ∞                |

|               | QIOR      | (EBh) 1110 1011                       | Quad I/O High Performance Read                                                    | 3                     | 1                    | 2                   | 1 to ∞                |

|               | RDID      | (9Fh) 1001 1111                       | Read Identification                                                               | 0                     | 0                    | 0                   | 1 to 81               |

|               | READ_ID   | (90h) 1001 0000                       | Read Manufacturer and Device Identification                                       | 3                     | 0                    | 0                   | 1 to ∞                |

| Maita Cantual | WREN      | (06h) 0000 0110                       | Write Enable                                                                      | 0                     | 0                    | 0                   | 0                     |

| Write Control | WRDI      | (04h) 0000 0100                       | Write Disable                                                                     | 0                     | 0                    | 0                   | 0                     |

|               | P4E       | (20h) 0010 0000                       | 4 KB Parameter Sector Erase                                                       | 3                     | 0                    | 0                   | 0                     |

|               | P8E       | (40h) 0100 0000                       | 8 KB (two 4KB) Parameter Sector Erase                                             | 3                     | 0                    | 0                   | 0                     |

| Erase         | SE        | (D8h) 1101 1000                       | 64KB Sector Erase                                                                 | 3                     | 0                    | 0                   | 0                     |

|               | BE        | (60h) 0110 0000 or<br>(C7h) 1100 0111 | Bulk Erase                                                                        | 0                     | 0                    | 0                   | 0                     |

| Duaguaga      | PP        | (02h) 0000 0010                       | Page Programming                                                                  | 3                     | 0                    | 0                   | 1 to 256              |

| Program QPP   | QPP       | (32h) 0011 0010                       | Quad Page Programming                                                             | 3                     | 0                    | 0                   | 1 to 256              |

|               | RDSR      | (05h) 0000 0101                       | Read Status Register                                                              | 0                     | 0                    | 0                   | 1 to ∞                |

| Status &      | WRR       | (01h) 0000 0001                       | Write (Status & Configuration) Register                                           | 0                     | 0                    | 0                   | 1 to 2                |

| Configuration | RCR       | (35h) 0011 0101                       | Read Configuration Register (CFG)                                                 | 0                     | 0                    | 0                   | 1 to ∞                |

| Register      | CLSR      | (30h) 0011 0000                       | Reset the Erase and Program Fail Flag (SR5 and SR6) and restore normal operation) | 0                     | 0                    | 0                   | 0                     |

|               | DP        | (B9h) 1011 1001                       | Deep Power-Down                                                                   | 0                     | 0                    | 0                   | 0                     |

| Power Saving  |           | (ABh) 1010 1011                       | Release from Deep Power-Down Mode                                                 | 0                     | 0                    | 0                   | 0                     |

| . Swer Gaving | RES       | (ABh) 1010 1011                       | Release from Deep Power-Down and Read<br>Electronic Signature                     | 0                     | 0                    | 3                   | 1 to ∞                |

| OTP           | OTPP      | (42h) 0100 0010                       | Program one byte of data in OTP memory space                                      | 3                     | 0                    | 0                   | 1                     |

| UIP           | OTPR      | (4Bh) 0100 1011                       | Read data in the OTP memory space                                                 | 3                     | 0                    | 1                   | 1 to ∞                |

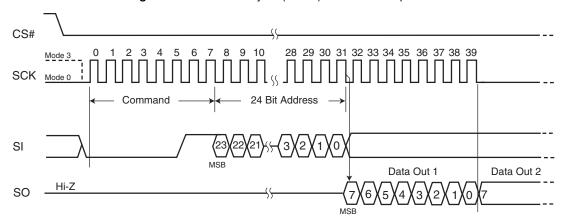

## 9.1 Read Data Bytes (READ)

The Read Data Bytes (READ) command reads data from the memory array at the frequency ( $f_R$ ) presented at the SCK input, with a maximum speed of 40 MHz. The host system must first select the device by driving CS# low. The READ command is then written to SI, followed by a 3 byte address (A23-A0). Each bit is latched on the rising edge of SCK. The memory array data, at that address, are output serially on SO at a frequency  $f_R$ , on the falling edge of SCK.

Figure 9.1 and Table 9.1 on page 23 detail the READ command sequence. The first address byte specified can start at any location of the memory array. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single READ command. When the highest address is reached, the address counter reverts to 00000h, allowing the read sequence to continue indefinitely.

The READ command is terminated by driving CS# high at any time during data output. The device rejects any READ command issued while it is executing a program, erase, or Write Registers operation, and continues the operation uninterrupted.

Figure 9.1 Read Data Bytes (READ) Command Sequence

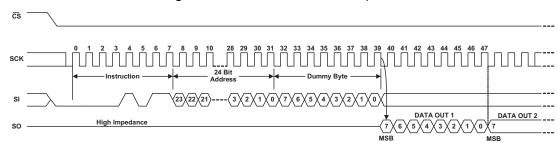

## 9.2 Read Data Bytes at Higher Speed (FAST\_READ)

The FAST\_READ command reads data from the memory array at the frequency ( $f_C$ ) presented at the SCK input, with a maximum speed of 104 MHz. The host system must first select the device by driving CS# low. The FAST\_READ command is then written to SI, followed by a 3 byte address (A23-A0) and a dummy byte. Each bit is latched on the rising edge of SCK. The memory array data, at that address, are output serially on SO at a frequency  $f_C$ , on the falling edge of SCK.

The FAST\_READ command sequence is shown in Figure 9.2 and Table 9.1 on page 23. The first address byte specified can start at any location of the memory array. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single FAST\_READ command. When the highest address is reached, the address counter reverts to 000000h, allowing the read sequence to continue indefinitely.

The FAST\_READ command is terminated by driving CS# high at any time during data output. The device rejects any FAST\_READ command issued while it is executing a program, erase, or Write Registers operation, and continues the operation uninterrupted.

Figure 9.2 Read Data Bytes at Higher Speed (FAST\_READ) Command Sequence

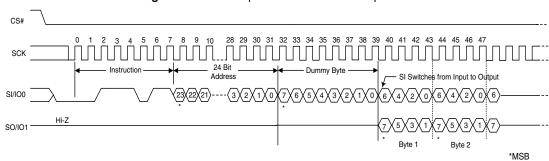

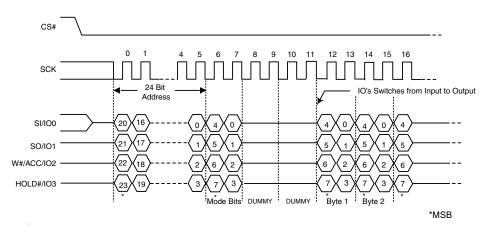

## 9.3 Dual Output Read Mode (DOR)

The Dual Output Read instruction is similar to the FAST\_READ instruction, except that the data is shifted out 2 bits at a time using 2 pins (SI/IO0 and SO/IO1) instead of 1 bit, at a maximum frequency of 80 MHz. The Dual Output Read mode effectively doubles the data transfer rate compared to the FAST\_READ instruction.

The host system must first select the device by driving CS# low. The Dual Output Read command is then written to SI, followed by a 3-byte address (A23-A0) and a dummy byte. Each bit is latched on the rising edge of SCK. Then the memory contents, at the address that is given, are shifted out two bits at a time through the IO0 (SI) and IO1 (SO) pins at a frequency f<sub>C</sub> on the falling edge of SCK.

The Dual Output Read command sequence is shown in Figure 9.3 and Table 9.1 on page 23. The first address byte specified can start at any location of the memory array. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single Dual Output Read command. When the highest address is reached, the address counter reverts to 00000h, allowing the read sequence to continue indefinitely.

It is important that the I/O pins be set to high-impedance prior to the falling edge of the first data out clock.

The Dual Output Read command is terminated by driving CS# high at any time during data output. The device rejects any Dual Output Read command issued while it is executing a program, erase, or Write Registers operation, and continues the operation uninterrupted.

Figure 9.3 Dual Output Read Instruction Sequence

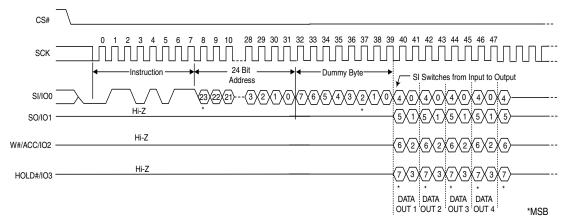

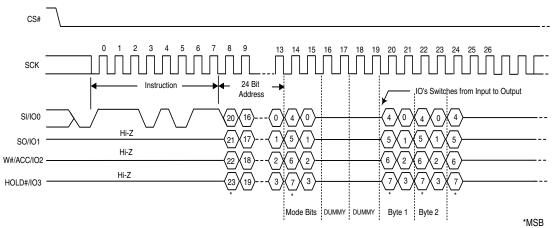

## 9.4 Quad Output Read Mode (QOR)

The Quad Output Read instruction is similar to the FAST\_READ instruction, except that the data is shifted out 4 bits at a time using 4 pins (SI/IO0, SO/IO1, W#/ACC/IO2 and HOLD#/IO3) instead of 1 bit, at a maximum frequency of 80 MHz. The Quad Output Read mode effectively doubles the data transfer rate compared to the Dual Output Read instruction, and is four times the data transfer rate of the FAST\_READ instruction.

The host system must first select the device by driving CS# low. The Quad Output Read command is then written to SI, followed by a 3-byte address (A23-A0) and a dummy byte. Each bit is latched on the rising edge of SCK. Then the memory contents, at the address that are given, are shifted out four bits at a time through IO0 (SI), IO1 (SO), IO2 (W#/ACC), and IO3 (HOLD#) pins at a frequency f<sub>C</sub> on the falling edge of SCK.

The Quad Output Read command sequence is shown in Figure 9.4 and Table 9.1 on page 23. The first address byte specified can start at any location of the memory array. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single Quad Output Read command. When the highest address is reached, the address counter reverts to 00000h, allowing the read sequence to continue indefinitely.

It is important that the I/O pins be set to high-impedance prior to the falling edge of the first data out clock.

The Quad Output Read command is terminated by driving CS# high at any time during data output. The device rejects any Quad Output Read command issued while it is executing a program, erase, or Write Registers operation, and continues the operation uninterrupted.

The Quad bit of Configuration Register must be set (CR Bit1 = 1) to enable the Quad mode capability of the S25FL device.

Figure 9.4 Quad Output Read Instruction Sequence

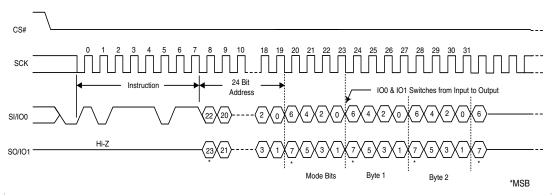

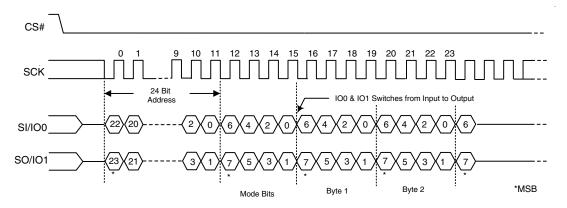

## 9.5 DUAL I/O High Performance Read Mode (DIOR)

The Dual I/O High Performance Read instruction is similar to the Dual Output Read instruction, except that it improves throughput by allowing input of the address bits (A23-A0) using 2 bits per SCK via two input pins (SI/IO2 and SO/IO1), at a maximum frequency of 80 MHz.

The host system must first select the device by driving CS# low. The Dual I/O High Performance Read command is then written to SI, followed by a 3-byte address (A23-A0) and a 1-byte Mode instruction, with two bits latched on the rising edge of SCK. Then the memory contents, at the address that is given, are shifted out two bits at a time through IO0 (SI) and IO1 (SO).

The DUAL I/O High Performance Read command sequence is shown in Figure 9.5 and Table 9.1 on page 23. The first address byte specified can start at any location of the memory array. The device automatically increments to the next higher address after each byte of data is output. The entire memory array can therefore be read with a single DUAL I/O High Performance Read command. When the highest address is reached, the address counter reverts to 00000h, allowing the read sequence to continue indefinitely.

In addition, address jumps can be done without exiting the Dual I/O High Performance Mode through the setting of the Mode bits (after the Address (A23-0) sequence, as shown in Figure 9.5). This added feature removes the need for the instruction sequence and greatly improves code execution (XIP). The upper nibble (bits 7-4) of the Mode bits control the length of the next Dual I/O High Performance instruction through the inclusion or exclusion of the first byte instruction code. The lower nibble (bits 3-0) of the Mode bits are DON'T CARE ("x"). If the Mode bits equal Axh, then the device remains in Dual I/O High Performance Read Mode and the next address can be entered (after CS# is raised high and then asserted low) without requiring the BBh instruction opcode, as shown in Figure 9.6, thus eliminating eight cycles for the instruction sequence. However, if the Mode bits are any value other than Axh, then the next instruction (after CS# is raised high and then asserted low) requires the instruction sequence, which is normal operation. The following sequences will release the device from Dual I/O High Performance Read mode; after which, the device can accept standard SPI instructions:

- 1. During the Dual I/O High Performance Instruction Sequence, if the Mode bits are any value other than Axh, then the next time CS# is raised high and then asserted low, the device will be released from Dual I/O High Performance Read mode.

- Furthermore, during any operation, if CS# toggles high to low to high for eight cycles (or less) and data input (IO0 & IO1) are not set for a valid instruction sequence, then the device will be released from Dual I/O High Performance Read mode.

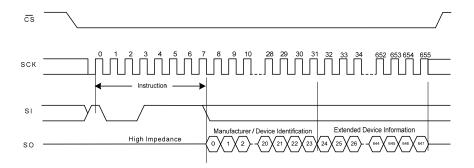

It is important that the I/O pins be set to high-impedance prior to the falling edge of the first data out clock.